# H261-Z60

Dual SP3 socket motherboard for the AMD EPYC Series Processor family

## Service Guide

Rev. 1.0

#### Copyright

© 2018 GIGA-BYTE TECHNOLOGY CO., LTD. All rights reserved.

The trademarks mentioned in this manual are legally registered to their respective owners.

#### Disclaimer

Information in this manual is protected by copyright laws and is the property of GIGABYTE. Changes to the specifications and features in this manual may be made by GIGABYTE without prior notice. No part of this manual may be reproduced, copied, translated, transmitted, or published in any form or by any means without GIGABYTE's prior written permission.

#### **Documentation Classifications**

In order to assist in the use of this product, GIGABYTE provides the following types of documentations:

For detailed product information, carefully read the User's Manual.

For more information, visit our website at:

http://b2b.gigabyte.com

Join our server forum to discuss our products and get technical assistance at:

forum.b2b.gigabyte.com

https://www.facebook.com/gigabyteserver

## Conventions

The following conventions are used in this user's guide:

|          | NOTE!                                            |

|----------|--------------------------------------------------|

| =]       | Gives bits and pieces of additional              |

|          | information related to the current topic.        |

|          | CAUTION!                                         |

| <u> </u> | Gives precautionary measures to                  |

|          | avoid possible hardware or software problems.    |

| A        | WARNING!                                         |

|          | Alerts you to any damage that might              |

|          | result from doing or not doing specific actions. |

#### **Server Warnings and Cautions**

Before installing a server, be sure that you understand the following warnings and cautions.

#### WARNING!

To reduce the risk of electric shock or damage to the equipment:

- Do not disable the power cord grounding plug. The grounding plug is an important safety feature

- Plug the power cord into a grounded (earthed) electrical outlet that is easily accessible at all times.

- Unplug the power cord from the power supply to disconnect power to the equipment.

- Do not route the power cord where it can be walked on or pinched by items placed against it.

Pay particular attention to the plug, electrical outlet, and the point where the cord extends from the server.

#### WARNING!

To reduce the risk of personal injury from hot surfaces, allow the drives and the internal system components to cool before touching them.

#### WARNING!

This server is equipped with high speed fans. Keep away from hazardous moving fan blades during servicing.

#### **CAUTION!**

- Do not operate the server for long periods with the access panel open or removed. Operating the server in this manner results in improper airflow and improper cooling that can lead to thermal damage.

- · Danger of explosion if battery is incorrectly replaced.

- Replace only with the same or equivalent type recommended by the manufacturer.

- Dispose of used batteries according to the manufacturer's instructions.

#### Electrostatic Discharge (ESD)

ESD CAN DAMAGE DRIVES, BOARDS, AND OTHER PARTS. WE RECOMMEND THAT YOU PERFORM ALL PROCEDURES AT AN ESD WORKSTATION. IF ONE IS NOT AVAILABLE, PROVIDE SOME ESD PROTECTION BY WEARING AN ANTI-STATIC WRIST STRAP ATTACHED TO CHASSIS GROUND -- ANY UNPAINTED METAL SURFACE -- ON YOUR SERVER WHEN HANDLING PARTS.

Always handle boards carefully. They can be extremely sensitive to ESD. Hold boards only by their edges without any component and pin touching. After removing a board from its protective wrapper or from the system, place the board component side up on a grounded, static free surface. Use a conductive foam pad if available but not the board wrapper. Do not slide board over any surface.

**System power on/off:** To remove power from system, you must remove the system from rack. Make sure the system is removed from the rack before opening the chassis, adding, or removing any non hot-plug components.

**Hazardous conditions, devices and cables:** Hazardous electrical conditions may be present on power, telephone, and communication cables. Turn off the system and discon-nect the cables attached to the system before servicing it. Otherwise, personal injury or equipment damage can result

**Electrostatic discharge (ESD) and ESD protection:** ESD can damage drives, boards, and other parts. We recommend that you perform all procedures in this chapter only at an ESD workstation. If one is not available, provide some ESD protection by wearing an antistatic wrist strap attached to chassis ground (any unpainted metal surface on the server) when handling parts.

**ESD and handling boards:** Always handle boards carefully. They can be extremely sensi-tive to electrostatic discharge (ESD). Hold boards only by their edges. After removing a board from its protective wrapper or from the system, place the board component side up on a grounded, static free surface. Use a conductive foam pad if available but not the board wrapper. Do not slide board over any surface.

**Installing or removing jumpers:** A jumper is a small plastic encased conductor that slips over two jumper pins. Some jumpers have a small tab on top that can be gripped with fin-gertips or with a pair of fine needle nosed pliers. If the jumpers do not have such a tab, take care when using needle nosed pliers to remove or install a jumper; grip the narrow sides of the jumper with the

pliers, never the wide sides. Gripping the wide sides can dam-age the contacts inside the jumper, causing intermittent problems with the function con-trolled by that jumper. Take care to grip with, but not squeeze, the pliers or other tool used to remove a jumper, or the pins on the board may bend or break.

## CAUTION!

Risk of explosion if battery is replaced incorrectly or with an incorrect type. Replace the battery only with the same or equivalent type recommended by the manufacturer. Dispose of used batteries according to the manufacturer's instructions.

## **Table of Contents**

| Chapter 1 | Hard  | ware | e Installation                            | 10 |

|-----------|-------|------|-------------------------------------------|----|

|           | 1-1   | Ins  | tallation Precautions                     | 10 |

|           | 1-2   | Pro  | duct Specifications                       | 11 |

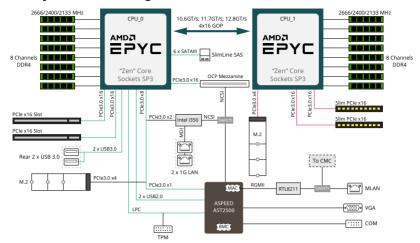

|           | 1-3   | Sys  | stem Block Diagram                        | 14 |

| Chapter 2 | Syste | em A | ppearance                                 | 16 |

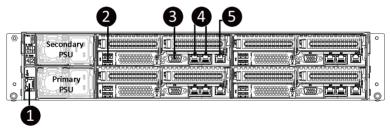

|           | 2-1   | Fro  | nt View                                   | 16 |

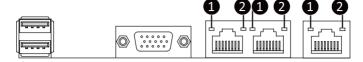

|           | 2-2   | Rea  | ar View                                   | 16 |

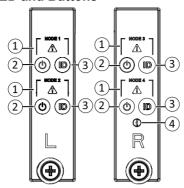

|           | 2-3   | Fro  | nt Panel LED and Buttons                  | 17 |

|           | 2-4   | Rea  | ar System LAN LEDs                        | 18 |

|           | 2-5   | Hai  | rd Disk Drive LEDs                        | 19 |

| Chapter 3 | Syste | em F | lardware Installation                     | 20 |

|           | 3-1   | Ins  | talling the Hard Disk Drive               | 21 |

|           | 3-2   | Rei  | moving the Node                           | 22 |

|           | 3-3   | Rei  | moving Chassis Cover                      | 23 |

|           | 3-4   | Rei  | moving and Installing the Fan Duct        | 24 |

|           | 3-5   | Rei  | moving and Installing the Heatsink        | 25 |

|           | 3-6   | Ins  | talling the CPU                           | 27 |

|           | 3-7   | Ins  | talling Memory                            | 28 |

|           | 3-7   | 7-1  | Eight Channel Memory Configuration        | 28 |

|           |       | 7-2  | Installing the Memory                     |    |

|           |       | 7-3  | DIMM Population Table                     |    |

|           | 3-8   |      | talling the PCI Expansion Card            |    |

|           | 3-9   |      | talling the OCP Card                      |    |

|           | 3-10  |      | placing the Fan Assembly                  |    |

|           | 3-11  |      | placing the Power Supply                  |    |

|           |       |      | Power Supply LED Behavior                 |    |

|           |       |      | placing Power Distribution Board Cage     |    |

|           | 3-13  |      | ble Routing                               |    |

| Chantar 1 |       |      | Hard Drive Back Plane Board Cable Routing |    |

| Chapter 4 |       |      | pard Components                           |    |

|           | 4-1   |      | therboard Components                      |    |

|           | 4-2   | Jur  | nper Setting                              | 43 |

| Chapter 5 | BIOS  | Set  | up                                         | 44  |

|-----------|-------|------|--------------------------------------------|-----|

|           | 5-1   | The  | e Main Menu                                | 46  |

|           | 5-2   | Adv  | /anced Menu                                | 48  |

|           | 5-2   | 2-1  | iSCSI Configuration                        | 49  |

|           | 5-2   | 2-2  | QLogic 577xx/578xx 10 Gb Ethernet BCM57810 | 50  |

|           | 5-2   | 2-3  | VLAN Configuration                         | 63  |

|           | 5-2   | 2-4  | CPU Configuration                          |     |

|           | 5-2   | 2-5  | SATA Configuration                         | 67  |

|           | 5-2   | 2-6  | USB Configuration                          | 68  |

|           | 5-2   | 2-7  | AST2500 Super IO Configuration             | 70  |

|           | 5-2   | 2-8  | Serial Port Console Redirection            | 73  |

|           | 5-2   | 2-9  | PCI Subsystem Settings                     | 78  |

|           | 5-2   | 2-10 | Network Stack                              | 80  |

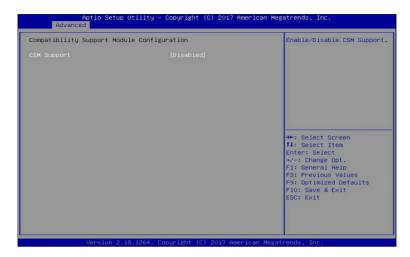

|           | 5-2   | 2-11 | CSM Configuration                          | 81  |

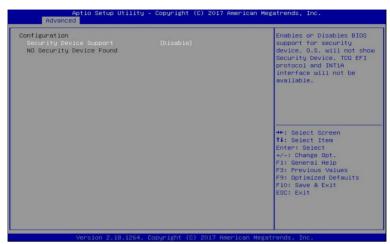

|           | 5-2   | 2-12 | Trusted Computing                          | 83  |

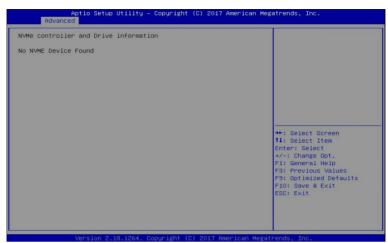

|           | 5-2   | 2-13 | NVMe Configuration                         | 84  |

|           | 5-3   | AM   | D CBS Menu                                 | 85  |

|           | 5-3   | 3-1  | Zen Common Options                         | 86  |

|           | 5-3   | 3-2  | DF Common Options                          | 89  |

|           | 5-3   | 3-3  | UMC Common Options                         | 90  |

|           | 5-3   | 3-4  | NBIO Common Options                        | 97  |

|           | 5-3   | 3-5  | FCH Common Options                         | 98  |

|           | 5-4   | Chi  | pset Setup Menu                            | 100 |

|           | 5-4   | 1-1  | North Bridge                               | 101 |

|           | 5-4   | 1-2  | Error Management                           | 104 |

|           | 5-5   | Ser  | ver Management Menu                        | 105 |

|           | 5-    | 5-1  | System Event Log                           | 107 |

|           | 5-    | 5-2  | View FRU Information                       | 108 |

|           | 5-5   | 5-3  | BMC Network Configuration                  | 109 |

|           | 5-8   | 5-4  | IPv6 BMC Network Configuration             | 111 |

|           | 5-6   | Sec  | curity Menu                                | 113 |

|           | 5-6-1 |      | Secure Boot                                | 114 |

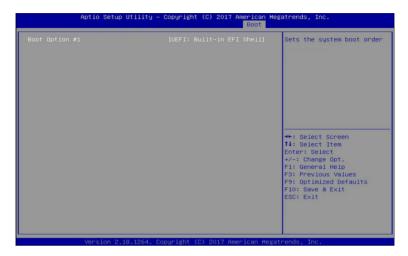

|           | 5-7   | Boo  | ot Menu                                    | 118 |

|           | 5-7   | 7-1  | UEFI NETWORK Drive BBS Priorities          | 120 |

|           | 5-7   | 7-2  | UEFI Application Boot Priorities           | 121 |

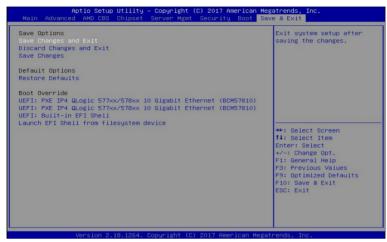

|           | 5-8   | Sav  | /e & Exit Menu                             | 122 |

|           | 5-9   | ABI  | L POST Codes                               | 123 |

|           | 5-9   | 9-1  | StartProcessorTestPoints                   | 123 |

|           | 5-9   | 9-2  | Memory test points                         | 123 |

|           | 5-9   | 9-3  | PMU Test Points                            | 123 |

|           | 5-9   | 9-4  | Original Post Code                         | 124 |

|     | 5-9-5  | CPU test points                                 | 125 |

|-----|--------|-------------------------------------------------|-----|

|     | 5-9-6  | Topology test points                            | 125 |

|     | 5-9-7  | Extended memory test point                      | 125 |

|     | 5-9-8  | Gnb Earlier init                                | 126 |

|     | 5-9-9  | PMU test points                                 | 129 |

|     | 5-9-10 | ABL0 test points                                | 129 |

|     | 5-9-11 | ABL5 test points                                | 129 |

| 5-′ | 10 Age | esa POST Codes                                  | 133 |

|     | 5-10-1 | Universal Post Code                             | 133 |

|     | 5-10-2 | [0xA1XX] For CZ only memory Postcodes           | 133 |

|     | 5-10-3 | S3 Interface Post Code                          | 136 |

|     | 5-10-4 | PMU Post Code                                   | 136 |

|     | 5-10-5 | [0xA5XX] assigned for AGESA PSP Module          | 136 |

|     | 5-10-6 | [0xA9XX, 0xAAXX] assigned for AGESA NBIO Module | 139 |

|     | 5-10-7 | [0xACXX] assigned for AGESA CCX Module          | 141 |

|     | 5-10-8 | [0xADXX] assigned for AGESA DF Module           | 142 |

|     | 5-10-9 | [0xAFXX] assigned for AGESA FCH Module          | 142 |

| 5-′ | 11 BIC | S POST Beep code (AMI standard)                 | 144 |

|     | 5-11-1 | PEI Beep Codes                                  | 144 |

|     | 5-11-2 | DXE Beep Codes                                  | 144 |

| 5-  | 12 BIC | S Recovery Instruction                          | 145 |

## **Chapter 1** Hardware Installation

#### 1-1 Installation Precautions

The motherboard/system contain numerous delicate electronic circuits and components which can become damaged as a result of electrostatic discharge (ESD). Prior to installation, carefully read the service guide and follow these procedures:

- Prior to installation, do not remove or break motherboard S/N (Serial Number) sticker or warranty sticker provided by your dealer. These stickers are required for warranty validation.

- Always remove the AC power by unplugging the power cord from the power outlet before installing or removing the motherboard or other hardware components.

- When connecting hardware components to the internal connectors on the motherboard, make sure they are connected tightly and securely.

- When handling the motherboard, avoid touching any metal leads or connectors.

- It is best to wear an electrostatic discharge (ESD) wrist strap when handling electronic components such as a motherboard, CPU or memory. If you do not have an ESD wrist strap, keep your hands dry and first touch a metal object to eliminate static electricity.

- Prior to installing the motherboard, please have it on top of an antistatic pad or within an

electrostatic shielding container.

- Before unplugging the power supply cable from the motherboard, make sure the power supply has been turned off.

- Before turning on the power, make sure the power supply voltage has been set according to the local voltage standard.

- Before using the product, please verify that all cables and power connectors of your hardware components are connected.

- To prevent damage to the motherboard, do not allow screws to come in contact with the motherboard circuit or its components.

- Make sure there are no leftover screws or metal components placed on the motherboard or within the computer casing.

- · Do not place the computer system on an uneven surface.

- Do not place the computer system in a high-temperature environment.

- Turning on the computer power during the installation process can lead to damage to system components as well as physical harm to the user.

- If you are uncertain about any installation steps or have a problem related to the use of the product, please consult a certified computer technician.

## 1-2 Product Specifications

| <b>€</b> CPU    | <ul> <li>AMD EPYC<sup>™</sup> 7000 series processor family</li> </ul> |

|-----------------|-----------------------------------------------------------------------|

|                 | CPU TDP up to 180W                                                    |

|                 | Per Node:                                                             |

| Socket          | 2 x SP3 Socket                                                        |

|                 | ▼ 2 x 5P3 500ket                                                      |

| Chipset         | System on Chip (SoC)                                                  |

| Memory          | Per Node:                                                             |

|                 | ◆ 16 x DIMM slots                                                     |

|                 | DDR4 memory supported only                                            |

|                 | 8-channel memory architecture                                         |

|                 | 8-channel RDIMM/LRDIMM                                                |

|                 | • 1.2V modules: 2667/2400/2133 MHz                                    |

| LAN LAN         | Per Node:                                                             |

|                 | ◆ 2 x 1Gb/s BASE-T LAN ports (Intel® I350-AT2)                        |

|                 | 1 x Dedicated management port                                         |

| Expansion Slots | Per node:                                                             |

|                 | • 2 x Half-length low-profile slot with PCIe x16 (Gen3 x16 bus)       |

|                 | 1 x OCP mezzanine slot with PCle Gen3 x16 bus                         |

|                 | • 2 x M.2 with PCle Gen3 x4 interface (1 from CPU0; 1 from CPU1)      |

|                 | Total:                                                                |

|                 | 8 x Half-length low-profile slot with PCIe x16                        |

|                 | 4 x OCP mezzanine slot with PCle Gen3 x16 bus                         |

|                 | 8 x M.2 with PCIe Gen3 x4 interface                                   |

| Video           | Integrated in Aspeed® AST2500                                         |

|                 | 2D Video Graphic Adapter with PCle bus interface                      |

|                 | • 1920x1200@60Hz 32bpp, DDR4 SDRAM                                    |

| Storage         | Per node:                                                             |

| Ciorago         | 6 x 2.5" SAS/SATA hot-swappable HDD/SSD bays                          |

|                 | V X 2.0 G/10/0/1/1/1/10t Gwappasio 1188/008 Bayo                      |

|                 | Total:                                                                |

|                 | 24 x 2.5" hot-swappable HDD/SSD bays                                  |

|                 | SAS card is required for SAS devices support                          |

| Internal        | Per Node:                                                             |

| Connectors      | ◆ 1 x COM header                                                      |

|                 | 1 x TPM header                                                        |

|                 | 1 x JTAG BMC header                                                   |

|                 | 1 x PLD header                                                        |

|                 | 1 x Function jumpers                                                  |

|                 | 5 x Function select                                                   |

|                 | 1 x IPMB connector                                                    |

|                 | · I A II W D COIIIICOLOI                                              |

| Front Panel    | Per node:                                                          |

|----------------|--------------------------------------------------------------------|

| LED/Buttons    | 1 x Power botton with LED                                          |

|                | • 1 x ID button with LED                                           |

|                | 1 x Enclosure LED                                                  |

|                | Total:                                                             |

|                | 4 x Power button with LED                                          |

|                | 4 x ID button with LED                                             |

|                | ◆ 4 x Status LED                                                   |

|                |                                                                    |

|                | *Only one CMC status LED per system                                |

| Rear Panel I/O | Per node:                                                          |

|                | • 2 x USB 3.0 ports                                                |

|                | <ul> <li>1 x 10/100/1000 Server Management LAN port</li> </ul>     |

|                | 2 x RJ-45 ports                                                    |

|                | Total:                                                             |

|                | • 8 x USB 3.0 ports                                                |

|                | <ul> <li>4 x 10/100/1000 Server Management LAN port</li> </ul>     |

|                | 8 x RJ-45 ports                                                    |

| TPM            | Per Node:                                                          |

|                | 1 x TPM header with LPC interface                                  |

|                | Optional TPM2.0 kit: CTM000                                        |

| System         | Aspeed® AST2500 management controller                              |

| Management     | Avocent® MergePoint IPMI 2.0 web interface:                        |

| Ŭ              | Network settings                                                   |

|                | Network security settings                                          |

|                | Hardware information                                               |

|                | Users control                                                      |

|                | Services settings                                                  |

|                | IPMI settings                                                      |

|                | Sessions control                                                   |

|                | ◆ LDAP settings                                                    |

|                | Power control                                                      |

|                | Fan profiles                                                       |

|                | Voltages, fans and temperatures monitoring                         |

|                | System event log                                                   |

|                | Events management (platform events, trap settings, email settings) |

|                | Serial Over LAN                                                    |

|                | vKVM & vMedia (HTML5)                                              |

| Form Factor    | Propriety Form Factor; 6.5" x 19.4",, 12 layers PCB                |

| Power Supply                    | <ul> <li>2 x 2200W redundant PSUs</li> <li>80 PLUS Platinum</li> <li>AC Input:         <ul> <li>100-127V~/ 14A, 47-63Hz</li> <li>200-240V~/ 12.6A, 47-63Hz</li> </ul> </li> </ul> |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | ◆ DC Output: - Max 1200W/ 100-127V~ +12.12V/ 95.6A +12Vsb/ 3.5A - Max 2200W/ 200-240V +12.12V/ 178.1A +12Vsb/ 3.5A                                                                |

| Ambient<br>Temperature          | <ul> <li>Operating temperature: 10°C to 35°C</li> <li>Operating humidity: 8-80% (non-condensing)</li> </ul>                                                                       |

| Relative<br>Humidity            | <ul> <li>Non-operating temperature: -40°C to 60°C</li> <li>Non-operating humidity: 20%-95% (non-condensing)</li> </ul>                                                            |

| System Dimension                | <ul> <li>2U 4 Nodes - Rear access</li> <li>440 x 87 x 820</li> </ul>                                                                                                              |

| * We reserves the right notice. | to make any changes to the product specifications and product-related information without prior                                                                                   |

## 1-3 System Block Diagram

## **Chapter 2** System Appearance

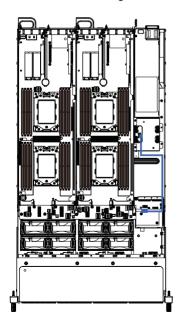

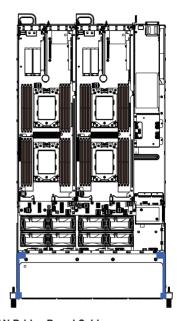

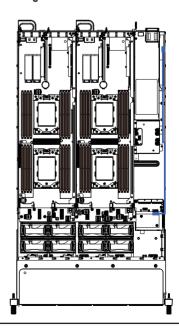

### 2-1 Front View

| No. | Decription                   |

|-----|------------------------------|

| 1.  | Front Panel LEDs and buttons |

Please Go to Chapter 2-3 Front Panel LED and Buttons for detail description of function LEDs.

### 2-2 Rear View

| No. | Decription                             |

|-----|----------------------------------------|

| 1.  | Chassis management Console port        |

| 2.  | USB 3.0 ports                          |

| 3.  | VGA port                               |

| 4.  | 1 Gb LAN port                          |

| 5.  | 10/100/1000 Server management LAN port |

## 2-3 Front Panel LED and Buttons

| No. | Name                  | Color   | Status                                        | Description                                         |  |  |

|-----|-----------------------|---------|-----------------------------------------------|-----------------------------------------------------|--|--|

|     |                       | Green   | On                                            | System is operating normally.                       |  |  |

|     |                       |         |                                               | Critical condition, may indicates:                  |  |  |

|     |                       |         | On                                            | System fan failure                                  |  |  |

|     |                       | Amber   |                                               | System temperature                                  |  |  |

| 1.  | System                | Allibei |                                               | Non-critical condition, may indicates:              |  |  |

|     | Status LED            |         | Blink                                         | Redundant power module failure                      |  |  |

|     |                       |         |                                               | Temperature and voltage issue                       |  |  |

|     |                       |         |                                               | Non-critical condition, may indicates:              |  |  |

|     |                       | N/A     | Off                                           | Redundant power module failure                      |  |  |

|     |                       |         |                                               | Temperature and voltage issue                       |  |  |

|     |                       | Green   | On                                            | System is powered on                                |  |  |

|     | Power button with LED | Green   | Blink System is in ACPI S1 state (sleep mode) |                                                     |  |  |

| 2.  |                       | N/A     | Off                                           | System is not powered on or in ACPI S5 state (power |  |  |

|     |                       |         |                                               | off)                                                |  |  |

|     |                       |         |                                               | System is in ACPI S4 state (hibernate mode)         |  |  |

| 3.  | ID Button             | Blue    | On                                            | System identification is active.                    |  |  |

| Э.  | with LED              | N/A     | Off                                           | System identification is disabled.                  |  |  |

|     |                       | Green   | On                                            | System is operating normally.                       |  |  |

|     |                       |         |                                               | Critical condition, may indicates:                  |  |  |

|     |                       |         |                                               | Power module failure                                |  |  |

|     |                       |         | On                                            | System fan failure                                  |  |  |

| 4.  | Enclosure             | Amber   |                                               | Power supply voltage issue                          |  |  |

|     |                       | Alliber |                                               | System temperature                                  |  |  |

|     |                       |         |                                               | Non-critical condition, may indicates:              |  |  |

|     |                       |         | Blink                                         | Redundant power module failure                      |  |  |

|     |                       |         |                                               | Temperature and voltage issue                       |  |  |

## 2-4 Rear System LAN LEDs

| No. | Name                          | Color  | Status | Description                                    |  |  |

|-----|-------------------------------|--------|--------|------------------------------------------------|--|--|

|     | 401.5                         | Yellow | On     | 1Gbps data rate                                |  |  |

| 1.  | 1GbE<br>Speed LED             | Green  | On     | 100 Mbps data rate                             |  |  |

|     |                               | N/A    | Off    | 10 Mbps data rate                              |  |  |

|     | 10hF                          |        | On     | Link between system and                        |  |  |

| 2.  | 1GbE<br>Link/<br>Activity LED | Green  |        | network or no access                           |  |  |

|     |                               |        | Blink  | Data transmission or receiving is occurring    |  |  |

|     | Houvity LLD                   | N/A    | Off    | No data transmission or receiving is occurring |  |  |

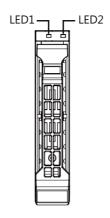

## 2-5 Hard Disk Drive LEDs

| RAID SKU                                                    |                                         | LED1  | Locate | HDD Fault | Rebuilding        | HDD<br>Access | HDD Present<br>(No Access) |

|-------------------------------------------------------------|-----------------------------------------|-------|--------|-----------|-------------------|---------------|----------------------------|

|                                                             | Disk LED<br>(LED on                     | Green | ON(*1) | OFF       |                   | BLINK (*2)    | OFF                        |

| N- DAIDf                                                    | Back Panel)                             | Amber | OFF    | OFF       |                   | OFF           | OFF                        |

| No RAID configuration<br>(via HBA, PCH)                     | Removed HDD Slot<br>(LED on Back Panel) | Green | ON(*1) | OFF       |                   |               |                            |

|                                                             |                                         | Amber | OFF    | OFF       |                   |               |                            |

| RAID configuration<br>(via HW RAID Card or<br>SW RAID Card) | Disk LED                                | Green | ON     | OFF       |                   | BLINK (*2)    | OFF                        |

|                                                             |                                         | Amber | OFF    | ON        | (Low Speed: 2 Hz) | OFF           | OFF                        |

|                                                             | Removed HDD Slot                        | Green | ON(*1) | OFF       | (*3)              |               |                            |

|                                                             |                                         | Amber | OFF    | ON        | (*3)              |               |                            |

#### NOTE:

<sup>\*3:</sup> If HDD is pulled out during rebuilding, the disk status of this HDD is regarded as faulty.

| LED 2 | HDD Present | No HDD |

|-------|-------------|--------|

| Green | ON          | OFF    |

<sup>\*1:</sup> Depends on HBA/Utility Spec.

<sup>\*2:</sup> Blink cycle depends on HDD's activity signal.

## Chapter 3 System Hardware Installation

#### Pre-installation Instructions

Computer components and electronic circuit boards can be damaged by discharges of static electricity. Working on computers that are still connected to a power supply can be extremely dangerous. Follow the simple guidelines below to avoid damage to your computer or injury to yourself.

- Always disconnect the computer from the power outlet whenever you are working inside the computer case.

- If possible, wear a grounded wrist strap when you are working inside the computer case.

Alternatively, discharge any static electricity by touching the bare metal system of the computer case, or the bare metal body of any other grounded appliance.

- Hold electronic circuit boards by the edges only. Do not touch the components on the board unless it is necessary to do so. Do not flex or stress the circuit board.

- Leave all components inside the static-proof packaging until you are ready to use the component for the installation.

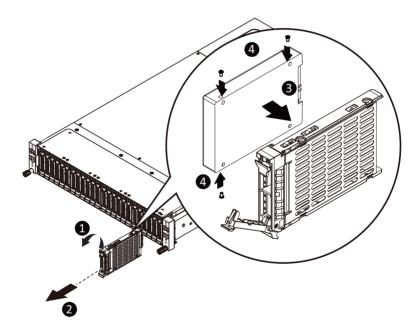

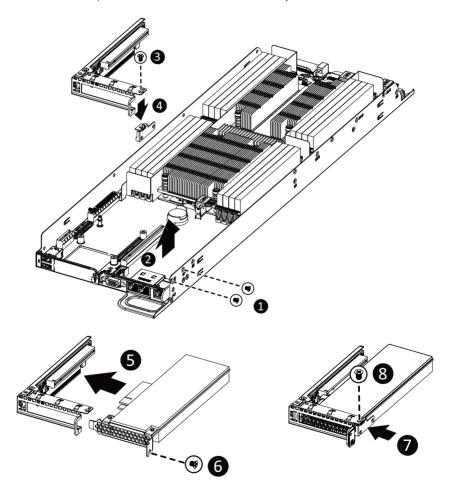

## 3-1 Installing the Hard Disk Drive

Read the following guidelines before you begin to install the Hard disk drive:

- · Take note of the drive tray orientation before sliding it out.

- · The tray will not fit back into the bay if inserted incorrectly.

- · Make sure that the HDD is connected to the HDD connector on the backplane.

#### Follow these instructions to install the Hard disk drive:

- 1. Press the release button.

- 2. Pull the locking lever to remove the HDD tray.

- 3. Pull apart the HDD tray.

- 4. Slide hard disk into the tray.

- 5. Push together to secure the hard drive.

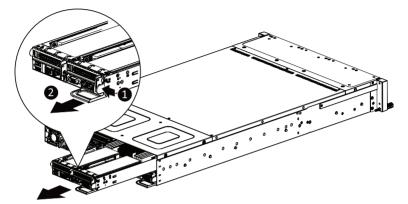

## 3-2 Removing the Node

Before you remove or install the node

Make sure the system is not turned on or connected to AC power.

#### Follow these instructions to remove a node:

Press the retaining clip on the right side of the node along the direction of the arrow, while pulling out the node using its handle.

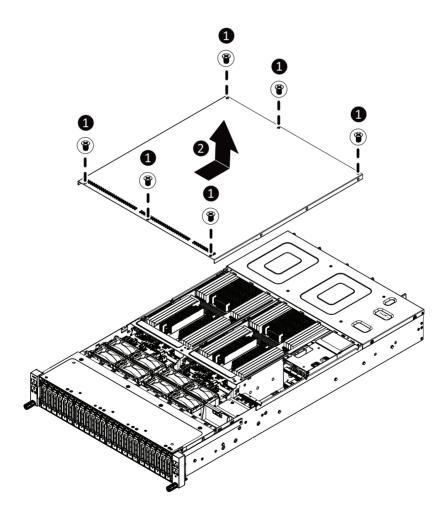

## 3-3 Removing Chassis Cover

Before you remove or install the system cover

· Make sure the system is not turned on or connected to AC power.

### Follow these instructions to remove the system cover:

- 1. Loosen and remove the six screws securing the back cover.

- 2. Slide the cover to the rear of the system and remove the cover in the direction of the arrow.

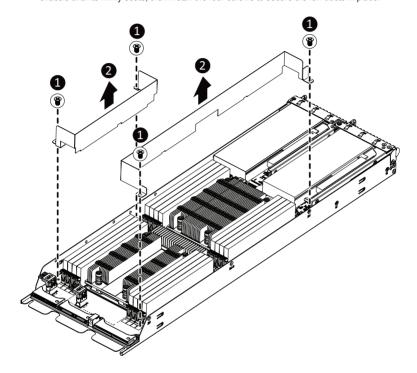

## 3-4 Removing and Installing the Fan Duct

Follow these instructions to remove/install the fan duct:

- 1. Remove the four screws securing the fan ducts.

- 2. Lift up to remove the fan ducts

- 3. To install the fan duct, align the fan duct with the guiding groove. Push down the fan duct into chassis until its firmly seats, then install the four screws to secure the fan ducts in place.

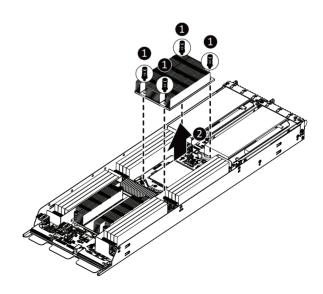

## 3-5 Removing and Installing the Heatsink

Read the following guidelines before you begin to install the heatsink:

- Always turn off the computer and unplug the power cord from the power outlet before installing the heatsink to prevent hardware damage.

- · Unplug all cables from the power outlets.

- · Disconnect all telecommunication cables from their ports.

- · Place the system unit on a flat and stable surface.

- · Open the system according to the instructions.

#### WARNING

Failure to properly turn off the server before you start installing components may cause serious damage. Do not attempt the procedures described in the following sections unless you are a qualified service technician.

#### Follow these instructions to remove the heatsink:

- 1. Loosen the four captive screws securing the heatsink to the system.

- 2 Lift and remove the heatsink

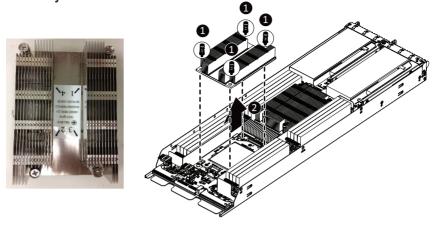

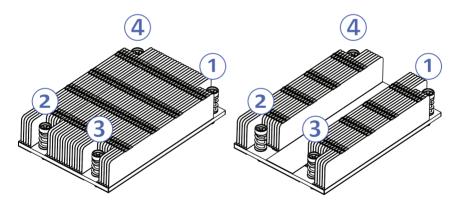

#### WARNING!

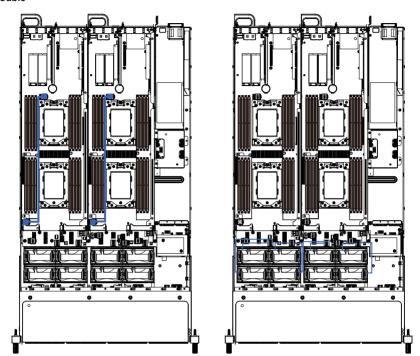

CPU0 and CPU1 use different CPU heatsinks. See the following images for using the correct heatsink.

Failure to observe the warning could result in damage to the equipment.

### **Primary CPU Heatsink**

## Secondary CPU Heatsink:

To install the heatsink, reverse the steps above while ensuring that you tighten the captive screws in sequential order  $(1\rightarrow 2\rightarrow 3\rightarrow 4)$  as seen in the image below.

## **Primary CPU Heatsink**

## Secondary CPU Heatsink:

## 3-6 Installing the CPU

Read the following guidelines before you begin to install the CPU:

- · Make sure that the motherboard supports the CPU.

- Always turn off the computer and unplug the power cord from the power outlet before installing the CPU to prevent hardware damage.

- · Unplug all cables from the power outlets.

- Disconnect all telecommunication cables from their ports.

- · Place the system unit on a flat and stable surface.

- · Open the system according to the instructions.

#### WARNING!

Failure to properly turn off the server before you start installing components may cause serious damage. Do not attempt the procedures described in the following sections unless you are a qualified service technician.

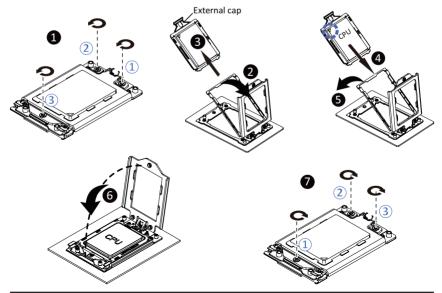

#### Follow these instructions to install the CPU:

- 1. Loosen the three captive screws in sequential order  $(1\rightarrow2\rightarrow3)$  securing the CPU cover.

- 2. Flip open the CPU cover.

- 3. Remove the CPU cap with CPU from the CPU frame using the handle on the CPU cap.

- 4. Using the handle on the CPU cap insert the new CPU cap with CPU installed into the CPU frame. NOTE: Ensure the CPU is installed in the CPU cap in the correct orientation, with the gold triangle on the CPU aligned to the top left corner of the CPU cap.

- 5. Flip the CPU frame with CPU installed into place in the CPU socket.

- 6. Flip the CPU cover into place over the CPU socket.

- 7. Tighten the CPU cover screws in sequential order  $(1\rightarrow2\rightarrow3)$  to secure the CPU cover in place.

## 3-7 Installing Memory

Read the following guidelines before you begin to install the memory:

- Make sure that the motherboard supports the memory. It is recommended that memory of the same capacity, brand, speed, and chips be used.

- Always turn off the computer and unplug the power cord from the power outlet before installing the memory to prevent hardware damage.

- Memory modules have a foolproof design. A memory module can be installed in only one direction. If you are unable to insert the memory, switch the direction.

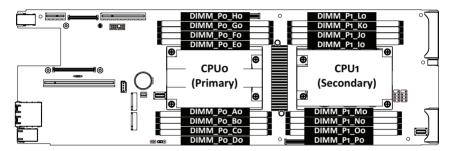

### 3-7-1 Eight Channel Memory Configuration

This motherboard provides 16 DDR4 memory sockets and supports Eight Channel Technology. After the memory is installed, the BIOS will automatically detect the specifications and capacity of the memory. Enabling eight Channel memory mode will be eight times of the original memory bandwidth.

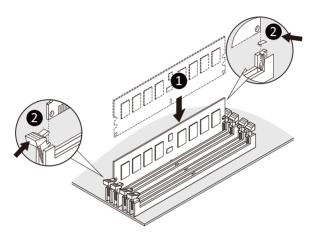

### 3-7-2 Installing the Memory

Before installing a memory module, make sure to turn off the computer and unplug the power cord from the power outlet to prevent damage to the memory module.

Be sure to install DDR4 DIMMs on this motherboard.

#### Follow these instructions to install the Memory:

- 1. Insert the DIMM memory module vertically into the DIMM slot, and push it down.

- 2. Close the plastic clip at both edges of the DIMM slots to lock the DIMM module.

- 3. Reverse the installation steps when you want to remove the DIMM module.

## 3-7-3 DIMM Population Table RDIMM Maximum Frequency Supported Tablel

| Slots | DIMMs<br>Populated | DIMM |           |               | Frequency (MT/s) |

|-------|--------------------|------|-----------|---------------|------------------|

|       |                    | 1R   | 2R<br>2DR | 4DR           | 1.2V             |

| 1     | 1                  | 1    |           |               | 2667             |

|       |                    |      | 1         |               | 2667             |

|       |                    |      |           | 1             | Not Supported    |

|       | 2                  | 1    |           |               | 2667             |

|       |                    |      | 1         |               | 2400             |

|       |                    |      |           | 1             | Not Supported    |

|       |                    | 2    |           |               | 2133             |

| 2     |                    | 1    | 1         |               | 2133             |

| 2     | 2                  |      | 2         |               | 2133             |

|       | 2                  |      |           | 2             | Not Supported    |

|       |                    | 1    |           | 1             | Not Supported    |

|       |                    | 1    | 1         | Not Supported |                  |

#### **3DS RDIMM Maximum Frequency Supported Table**

| Slote | DIMMs     | DIMM |              |      | Frequency (MT/s) |

|-------|-----------|------|--------------|------|------------------|

|       | Populated | NA   | 2S2R<br>2S4R | 4DR  | 1.2V             |

| 1 1   |           | 1    |              |      | Not Supported    |

|       | 1         |      | 1            |      | 2667             |

|       |           |      |              | 1    | Not Supported    |

| 1     |           | 1    |              |      | Not Supported    |

|       |           | 1    |              | 2400 |                  |

|       |           |      |              | 1    | Not Supported    |

|       | 2 2       | 2    |              |      | Not Supported    |

| 2     |           | 1    | 1            |      | Not Supported    |

|       |           |      | 2            |      | 1866             |

|       |           |      |              | 2    | Not Supported    |

|       |           | 1    |              | 1    | Not Supported    |

#### **LRDIMM Maximum Frequency Supported Table**

| Slots | DIMMs<br>Populated | DIMM |      |     | Frequency (MT/s) |

|-------|--------------------|------|------|-----|------------------|

|       |                    | 1R   | 2S4R | 4DR | 1.2V             |

| 1 1   |                    | 1    |      |     | Not Supported    |

|       | 1                  |      | 1    |     | 2667             |

|       |                    |      |      | 1   | 2667             |

|       | 2 2                | 1    |      |     | Not Supported    |

|       |                    |      | 1    |     | 2667             |

|       |                    |      |      | 1   | 2667             |

|       |                    | 2    |      |     | Not Supported    |

| 2     |                    | 1    | 1    |     | Not Supported    |

|       |                    |      | 2    |     | 2133             |

|       |                    |      |      | 2   | 2133             |

|       |                    | 1    |      | 1   | Not Supported    |

|       |                    |      | 1    | 1   | 2133             |

#### NOTE!

I 1R: 1 package rank of SDP DRAMs

I 2R: 2 package rank of SDP DRAMs

I 2DR: 2 package rank of DDP DRAMs

I 4DR: 2 package rank of DDP DRAMs

I 1S2R/1S4R/1S8R: 1 package rank of 2/4/8 high 3DS DRAMs

I 2S2R/2S4R/2S8R: 2 package rank of 2/4/8 high 3DS DRAMs

I DIMM must be populated in sequential alphabetic order, starting with bank A.

I When only one DIMM is used, it must be populated in memory slot A1.

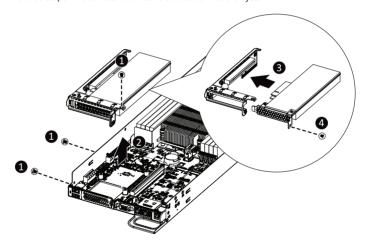

## 3-8 Installing the PCI Expansion Card

Voltages can be present within the server whenever an AC power source is connected.

This voltage is present even when the main power switch is in the off position. Ensure that the system is powered-down and all power sources have been disconnected from the server prior to installing a PCI card.

Failure to observe these warnings could result in personal injury or damage to equipment.

The PCI riser assembly does not include a riser card or any cabling as standard. To install

a PCI card, a riser card must be installed.

#### Follow these instructions to install the left PCI Expansion card:

- Remove the three screws securing the riser bracket to the system.

- 2. Lift up the riser bracket out of system.

- Align the PCI-E card to the riser guide slot and push in the direction of the arrow until the PCI-E card sits in the PCI card connector.

- 4. Secure the PCI-E card with a screw.

- 5. Reverse steps 1 3 to install the riser bracket back into the system.

#### Follow these instructions to install the right PCI Expansion card:

- 1. Remove the two screws on the riser bracket to the system.

- 2. Lift up the riser bracket out of system.

- 3. Remove the screw securing the side bracket to the riser bracket.

- 4. Remove the side bracket

- Align the PCI-E card to the riser guide slot and push in the direction of the arrow until the PCI-E card sits in the PCI card connector.

- 6. Secure the PCI-E card with a screw.

- Install the side bracket to the riser bracket.

- 8. Secure the side bracket to the riser bracket with a screw.

- 9. Reverse steps 1 2 to install the riser bracket back into the system.

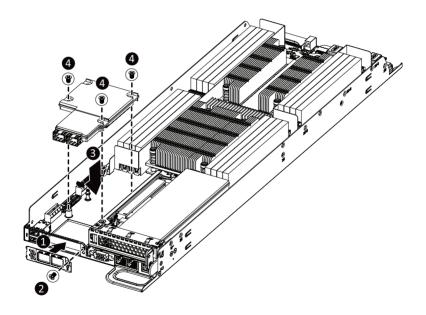

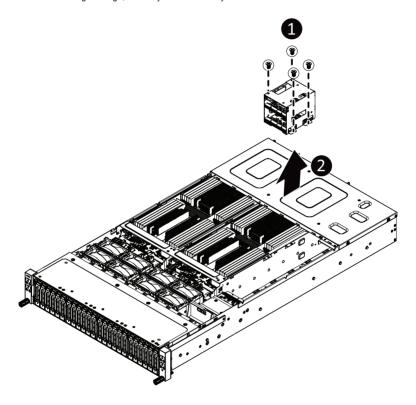

## 3-9 Installing the OCP Card

Voltages can be present within the server whenever an AC power source is connected.

This voltage is present even when the main power switch is in the off position. Ensure that the system is powered-down and all power sources have been disconnected from the server prior to installing a OCP card.

Failure to observe these warnings could result in personal injury or damage to equipment.

Before installing the OCP card the left PCI-E riser assembly must be first removed, see the <code>IInstalling</code> the PCI Expansion Card<sup>II</sup> section for instructions on removing the PCI-E riser assembly.

#### Follow these instructions to install the OCP card:

- Install the OCP card bracket.

- Secure the OCP card bracket with a screw.

- Align the OCP card to the connector on the system board and push in the direction of the arrow until the OCP card sits firmly in the system.

- Secure the OCP card with three screws.

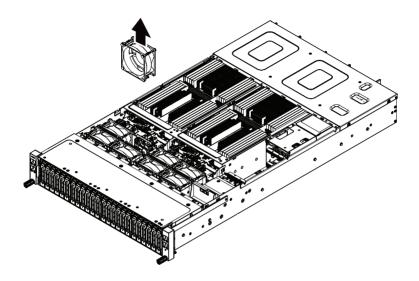

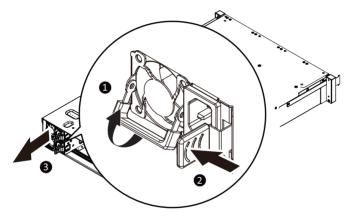

## 3-10 Replacing the Fan Assembly

Follow these instructions to replace the fan assembly:

- 1. Pull the fan ear outward.

- 2. Lift up the fan assembly from the chassis.

- 3. Reverse the previous steps to install the replacement fan assembly.

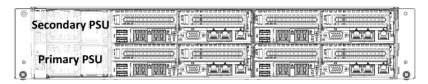

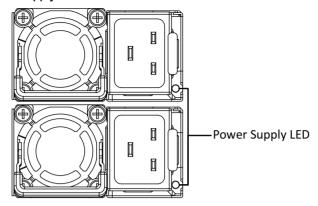

## 3-11 Replacing the Power Supply

Before you remove or install the system cover

· Make sure the system is not turned on or connected to AC power.

#### Follow these instructions to replace the power supply:

- Pull up the power supply handle and press the retaining clip on the right side of the power supply along the direction of the arrow. At the same time, pull out the power supply by using its handle.

- Insert the replacement power supply firmly into the chassis. Connect the AC power cord to the replacement power supply.

## 3-11-1 Power Supply LED Behavior

| State             | Description                                                                                            |

|-------------------|--------------------------------------------------------------------------------------------------------|

| Green On          | +12V output ON and OK                                                                                  |

| Off               | No AC power to all power supplies                                                                      |

| 0.5Hz Blink/Green | AC presents/Only +12VSB on (PS Off) Or PSU in Smart standby mode                                       |

| Amber             | AC cord unplugged, or AC power lost; with a second power supply in parallel still with AC input power. |

| 0.5Hz Blink/Amber | Power supply warning events where the power supply continues to operate; high power current, slow fan  |

| Amber             | Power supply critical event causing a shutdown; OTP, OCP, UVP, OVP, fan fail                           |

| 2Hz Blink/Green   | Power supply firmware updating                                                                         |

# 3-12 Replacing Power Distribution Board Cage

Before you remove or install the power distribution board cage:

· Make sure the system is not turned on or connected to AC power.

# Follow these instructions to remove the power distribution board cage:

- 1. Loosen and remove the four screws securing the cage.

- 2. While holding the cage, vertically lift it from the system.

# 3-13 Cable Routing

**System Power Cable**

Power Distribution Board Signal Cable

Front Switch Cable/Front LED Cable

**LAN Bridge Board Cable**

# On-Board SATA to HDD Back Plane Board System Fan Cable Cable

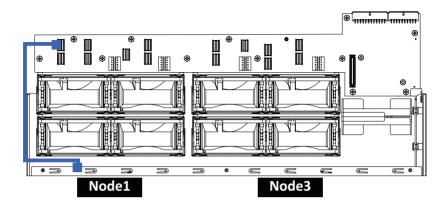

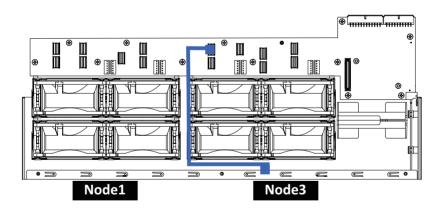

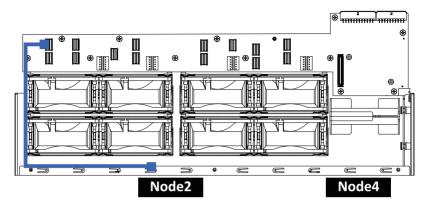

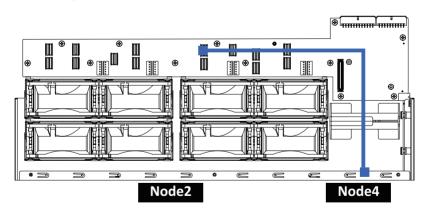

# 3-13-1 Hard Drive Back Plane Board Cable Routing HDD #0-5 Signal Cable

# HDD #12-17 Signal Cable

# HDD #18-23 Signal Cable

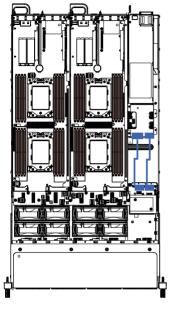

# **Chapter 4** Motherboard Components

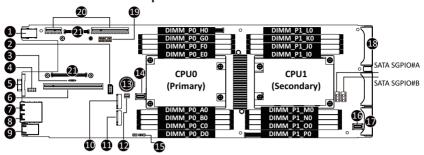

# 4-1 Motherboard Components

| Item | Description                          |  |  |

|------|--------------------------------------|--|--|

| 1    | USB 3.0 ports                        |  |  |

| 2    | IPMB connector                       |  |  |

| 3    | NCSI switch                          |  |  |

| 4    | Serial port connector                |  |  |

| 5    | VGA port                             |  |  |

| 6    | Riser slot #2 (Gen 3/x16 slot)       |  |  |

| 7    | Gigabit LAN port #2                  |  |  |

| 8    | Gigabit LAN port #1                  |  |  |

| 9    | Server management LAN port           |  |  |

| 10   | M.2 connector (CPU0)                 |  |  |

| 11   | M.2 connector (CPU1)                 |  |  |

| 12   | Function jumper switch               |  |  |

| 13   | System battery                       |  |  |

| 14   | Slimline SAS connector               |  |  |

| 15   | Clear CMOS jumper                    |  |  |

| 16   | Slimline SAS connector               |  |  |

| 17   | GF_1_1                               |  |  |

| 18   | GF_1_3                               |  |  |

| 19   | TPM connector                        |  |  |

| 20   | Riser slot #1 (Gen 3/x1 and x8 slot) |  |  |

| 21   | OCP mezzanine connector              |  |  |

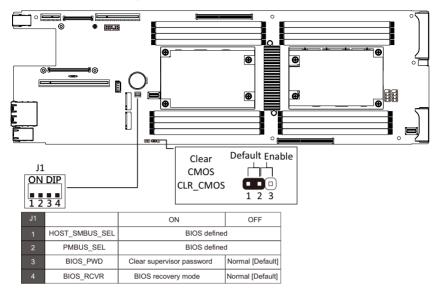

# 4-2 Jumper Setting

# Chapter 5 BIOS Setup

BIOS (Basic Input and Output System) records hardware parameters of the system in the EFI on the motherboard. Its major functions include conducting the Power-On Self-Test (POST) during system startup, saving system parameters and loading operating system, etc. BIOS includes a BIOS Setup program that allows the user to modify basic system configuration settings or to activate certain system features. When the power is turned off, the battery on the motherboard supplies the necessary power to the CMOS to keep the configuration values in the CMOS.

To access the BIOS Setup program, press the <Del> key during the POST when the power is turned on.

- BIOS flashing is potentially risky, if you do not encounter problems of using the current BIOS version, it is recommended that you don't flash the BIOS. To flash the BIOS, do it with caution. Inadequate BIOS flashing may result in system malfunction.

- It is recommended that you not alter the default settings (unless you need to) to prevent system

instability or other unexpected results. Inadequately altering the settings may result in system's

failure to boot. If this occurs, try to clear the CMOS values and reset the board to default values.

(Refer to the Exit section in this chapter or introductions of the battery/clearing CMOS jumper in

Chapter 1 for how to clear the CMOS values.)

# **BIOS Setup Program Function Keys**

| <←><→>          | Move the selection bar to select the screen                       |

|-----------------|-------------------------------------------------------------------|

| <↑><↓>          | Move the selection bar to select an item                          |

| <+>             | Increase the numeric value or make changes                        |

| <->             | Decrease the numeric value or make changes                        |

| <enter></enter> | Execute command or enter the submenu                              |

| <esc></esc>     | Main Menu: Exit the BIOS Setup program                            |

|                 | Submenus: Exit current submenu                                    |

| <f1></f1>       | Show descriptions of general help                                 |

| <f3></f3>       | Restore the previous BIOS settings for the current submenus       |

| <f9></f9>       | Load the Optimized BIOS default settings for the current submenus |

| <f10></f10>     | Save all the changes and exit the BIOS Setup program              |

|                 |                                                                   |

### ■ Main

This setup page includes all the items in standard compatible BIOS.

### Advanced

This setup page includes all the items of AMI BIOS special enhanced features.

(ex: Auto detect fan and temperature status, automatically configure hard disk parameters.)

### AMD CBS

This setup page includes the common items for configuration of AMD motherboard-related information.

### Chipset

This setup page includes all the submenu options for configuring the function of processor, network, North Bridge, South Bridge, and System event logs.

### ■ Server Management

Server additional features enabled/disabled setup menus.

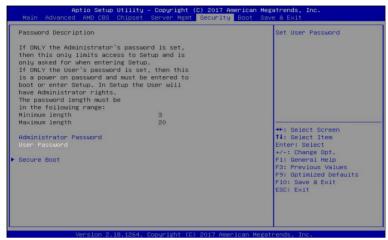

# ■ Security

Change, set, or disable supervisor and user password. Configuration supervisor password allows you to restrict access to the system and BIOS Setup.

A supervisor password allows you to make changes in BIOS Setup.

A user password only allows you to view the BIOS settings but not to make changes.

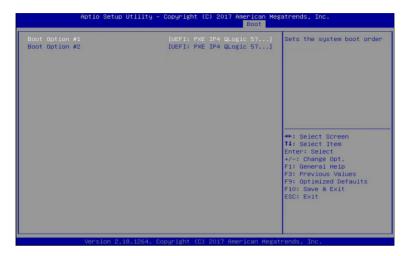

### ■ Boot

This setup page provides items for configuration of boot sequence.

### Save & Exit

Save all the changes made in the BIOS Setup program to the CMOS and exit BIOS Setup. (Pressing <F10> can also carry out this task.)

Abandon all changes and the previous settings remain in effect. Pressing <Y> to the confirmation message will exit BIOS Setup. (Pressing <Esc> can also carry out this task.)

# 5-1 The Main Menu

Once you enter the BIOS Setup program, the Main Menu (as shown below) appears on the screen. Use arrow keys to move among the items and press <Enter> to accept or enter other sub-menu.

# Main Menu Help

The on-screen description of a highlighted setup option is displayed on the bottom line of the Main Menu.

### Submenu Help

While in a submenu, press <F1> to display a help screen (General Help) of function keys available for the menu. Press <Esc> to exit the help screen. Help for each item is in the Item Help block on the right side of the submenu.

When the system is not stable as usual, select the **Restore Defaults** item to set your system to its defaults.

The BIOS Setup menus described in this chapter are for reference only and may differ by BIOS version.

### Project Name

Displays the project name information.

### Project Version

Displays version number of the BIOS setup utility.

### Build Date and Time

Displays the date and time when the BIOS setup utility was created.

- → BMC Information<sup>(Note)</sup>

- → BMC Firmware Version<sup>(Note)</sup>

Displays BMC firmware version information.

- Onboard LAN Information

- → LAN1 MAC Address<sup>(Note)</sup>

Displays LAN1 MAC address information.

### → LAN2 MAC Address<sup>(Note)</sup>

Displays LAN2 MAC address information.

# → Total Memory<sup>(Note)</sup>

Displays the information for the installed memory size.

#

Displays the information for the installed memory speed.

# ☐ System Date

Sets the date following the weekday-month-day-year format.

## System Time

Sets the system time following the hour-minute-second format.

# 5-2 Advanced Menu

The Advanced menu display submenu options for configuring the function of various hardware components. Select a submenu item, then press [Enter] to access the related submenu screen.

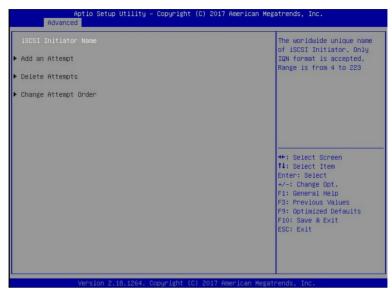

# 5-2-1 iSCSI Configuration

Press [Enter] for configuration of advanced items.

Delete Attempts

Press [Enter] for configuration of advanced items.

Change Attempt Order

Press [Enter] for configuration of advanced items.

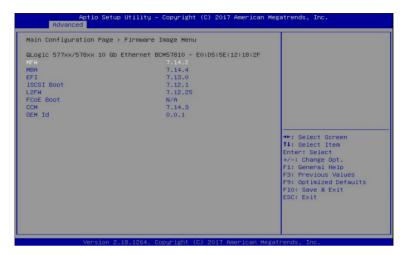

# 5-2-2 QLogic 577xx/578xx 10 Gb Ethernet BCM57810

- Main Configuration Page

- → Firmware Image Menu

Press [Enter] to view device firmware version information.

Device Hardware Configuration Menu

Press [Enter] to configure device and port specific parameters.

MBA Configuration Menu

Press [Enter] to configure Multiple Boot Agent (MBA) parameters.

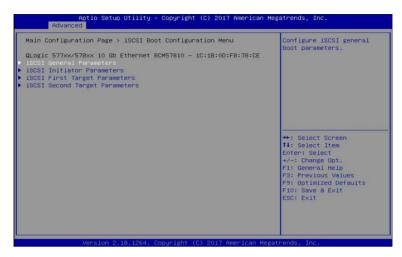

iSCSI Boot Configuration Menu

Press [Enter] to configure iSCSI boot parameters.

## → Multi-Function Mode

Virtualization mode configuration. System must be rebooted in order for changes to take effect. Options available: SF/SR-IOV. Default setting is **SF**.

### → Blink LEDs

Blink LEDs for a duration up to 15 seconds. Default setting is **0**.

# ☐ Chip Type

Displays the chip type.

### → PCI Device ID

Displays the PCI device ID.

### → Bus: Device: Function

Displays the bus number, device number, and function number.

### → Link Status

Displays the link status.

### → Parameter MAC Address

Displays the Permanent MAC Address.

### ▽ Virtual MAC Address

Displays the Virtual MAC Address.

# 5-2-2-1 Firmware Image Menu

#

Displays the device's firmware version information.

# 5-2-2-2 Device Hardware Configuration Menu

#

Configures the device and port specific parameters. Please refer to help text defined per configurable parameter for more information.

### → DCB Protocol

Enable/Disable the DCB Protocol.

Options available: Enabled/Disabled. Default setting is Enabled.

## → Number of VFs per PF

Displays the number of VFs per PF in multiple of 8 (0 to 64).

### Max PF MSI-X Vectors

Displays the maximum number of PF MSI-X Vectors. (0 to 64).

### → UEFI Boot Mode

Specifies Driver Boot Mode in UEFI environment.

Default setting is UNDI.

### → MFW Crash Dump Feature

Enables MFW bootcode to collect critical device and system information during unanticipated system crash.

Options available: Enabled/Disabled. Default setting is Enabled.

# 5-2-2-3 MBA Configuration Menu

Main Configuration Page > MBA Configuration Menu

Configures the Multiple Boot Agent (MBA) parameters.

Configures the Multiple Boot Agent (MBA) parameters.

Configures the Multiple Boot Agent (MBA) parameters.

□ Legacy Boot Protocol

Selects a non-UEFI Boot Protocol to be used.

Options available: PXE/iSCSI/None. Default setting is **None**.

### → Boot Strap Type

Selects the BIOS interrupt call type.

Auto Detect: Auto Detect interrupt type; BBS: BIOS Boot Specification; Int 18h: Interrupt vector to execute cassette BASIC: Int 19h: BIOS Interrupt vector used to load OS.

Options available: Auto Detect/BBS/Int 18h/Int 19h. Default setting is Auto Detect.

### → Hide Setup Prompt

Configures whether Setup Prompt is displayed during ROM initialization.

Options available: Enabled/Disabled. Default setting is Disabled.

### Setup Key Stroke

Configure key strokes to invoke configuration menu.

Options available: Ctrl-S/Ctrl-B. Default setting is Ctrl-S.

### Banner Message Timeout

Selects the timeout value. (0 defaults to 4 seconds, 15 is no delay, 1-14 is timeout value in seconds). Default setting is **5**.

###

Configures the link speed.

Default setting is 10 Gbps Full.

### → Wake On LAN

Configures Wake on LAN (WOL). This setting is per port.

Options available: Enabled/Disabled. Default setting is Disabled.

### → VLAN Mode

Configures the virtual LAN mode.

Options available: Enabled/Disabled. Default setting is Disabled.

### ▽ VLAN ID (1..4094)

Displays the virtual LAN ID (1 to 4094).

### → Boot Retry Count

Selects the number of boot retries.

Options available: No Retry/1 Retry/2 Retries/3 Retries/4 Retries/5 Retries/6 Retries/Indefinite Retries. Default setting is **No Retry**.

# 5-2-2-4 iSCSI Boot Configuration Menu

# → Main Configuration Page > iSCSI Boot Configuration Menu

Configures the iSCSI boot parameters.

Press [Enter] for configuration of advanced items.

□ iSCSI Initiator Parameters

Press [Enter] for configuration of advanced items.

iSCSI First Target Parameters

Press [Enter] for configuration of advanced items.

□ iSCSI Second Target Parameters

Press [Enter] for configuration of advanced items.

### 5-2-2-4-1 iSCSI General Parameters

# Main Configuration Page > iSCSI Boot Configuration Menu > iSCSI General Parameters

Configures the iSCSI general boot parameters.

### → TCP/IP Parameters via DHCP

Acquires the TCP/IP configuration via DHCP.

Options available: Enabled/Disabled. Default setting is Enabled.

### → IP Autoconfiguration

Auto-configures the IP configuration.

Options available: Enabled/Disabled. Default setting is **Disabled**.

Please note that this item is configurable when TCP/IP Parameters via DHCP is set to Disabled.

###

Acquires the iSCSI parameters via DHCP.

Options available: Enabled/Disabled. Default setting is Enabled.

### ☐ CHAP Authentication

Enable/Disable the CHAP authentication.

Options available: Enabled/Disabled. Default setting is Disabled.

### Boot to Target

Enable/Disable booting to iSCSI target after log-on.

Options available: Disabled/Enabled/One Time Disabled. Default setting is Enabled.

### → DHCP Vendor ID

Press [Enter] to configures the DHCP vendor ID (up to 32 bytes long).

# □ Link Up Delay Time

Configures the link up to delay time in seconds (0..225).

# ☐ Use TCP Timestamp

Enable/Disable the TCP timestamp.

Options available: Enabled/Disabled. Default setting is Disabled.

## □ Target as first HDD

Enable/Disable target appears as a first hard disk drive (HDD) in the system.

Options available: Enabled/Disabled. Default setting is Disabled.

### LUN Busy Retry Count

Configures the number of retries in 2 second intervals when LUN is busy (0..60).

Default setting is 0.

### → IP Version

Displays the IP version supported. Modifying this parameter will reset all IP-related fields.

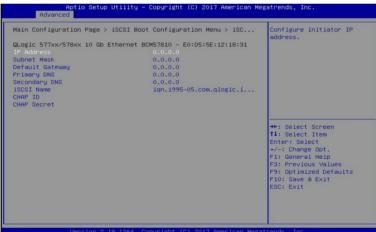

### 5-2-2-4-2 iSCSI Initiator Parameters

# Main Configuration Page > iSCSI Boot Configuration Menu > iSCSI Initiator Parameters

Configures the iSCSI initiator parameters.

→ IP Address

Configures initiator IP address.

→ Subnet Mask

Configures IP subnet mask.

Default Gateway

Configures default gateway IP address.

#

Configures the primary DNS IP address.

#

Configures the second DNS IP address.

##

Configures the iSCSI name.

## → CHAP ID

Configures the Challenge-Handshake Authentication Protocol (CHAP) ID (up to 128 characters in length).

# ☐ CHAP Secret

Configure the Challenge-Handshake Authentication Protocol (CHAP) Secret (12 to 16 characters in length).

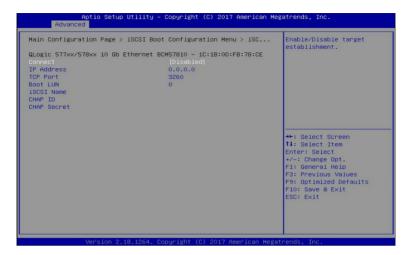

# 5-2-2-4-3 iSCSI First Target/Second Target Parameters

# Main Configuration Page > iSCSI Boot Configuration Menu > iSCSI First Target/ Second Target arameters

Configures the iSCSI first target parameters.

### → Connect

Enable/Disable the target establishment.

Options available: Enabled/Disabled. Default setting is **Disabled**.

### → IP Address

Configures the target IP address.

## → TCP Port

Configures the target TCP port number (13365535).

# → Boot LUN

Configure the target boot LUN number (0..255).

##

Configures the iSCSI name.

## → CHAP ID

Configures the Challenge-Handshake Authentication Protocol (CHAP) ID (up to 128 characters in length).

# ☐ CHAP Secret

Configure the Challenge-Handshake Authentication Protocol (CHAP) Secret (12 to 16 characters in length).

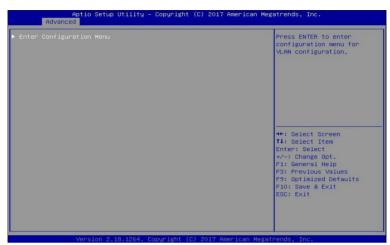

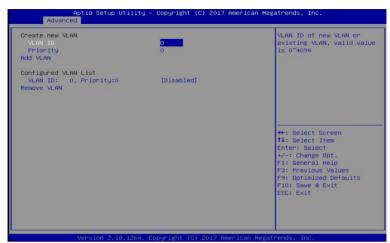

# 5-2-3 VLAN Configuration

# □ Enter Configuration Menu

Press [Enter] to enter configuration menu for VLAN configuration.

# 5-2-3-1 VLAN Configuration Menu

- → VLAN ID

Sets a VLAN ID of new VLAN or existing VLAN, valid value is 0 to 4094.

Priority

Sets the 802.1Q Priority, valid value is 0 to 7.

→ Add VLAN

Creates a new VLAN or update existing VLAN.

☐ Configured VLAN List

Displays the configured VLAN list information.

Options available: Enabled/Disabled. Default setting is Disabled.

Removes the selected VLANs.

Please note that this item is only executable when Configured VLAN List is set to Enabled, and once executed the Configured VLAN List will be updated accordingly.

# 5-2-4 CPU Configuration

# → CPU Configuration

### → SVM Mode

Enable/disable the CPU Virtualization.

Options available: Enabled/Disabled. Default setting is Enabled.

## → SMEE

Controls the Secure Memory Encryption Enable (SMEE) function. Options available: Enabled/Disabled. Default setting is **Enabled**.

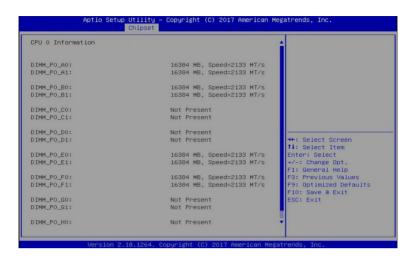

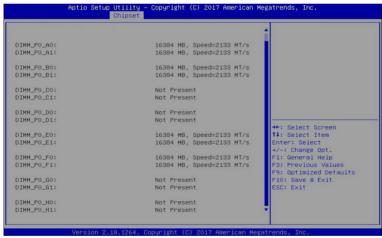

### → CPU 0 Information

Press [Enter] to view the memory information related to CPU 0.

## 5-2-4-1 CPU 0 Information

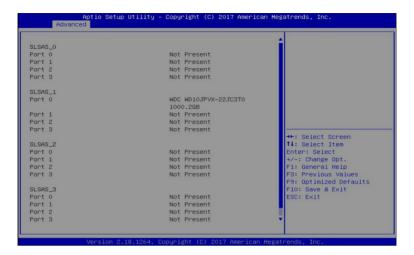

# 5-2-5 SATA Configuration

# 5-2-6 USB Configuration

# → USB Configuration

### → USB Controllers:

Displays the supported USB controllers.

### → USB Devices:

Displays the USB devices connected to the system.

### Legacy USB Support

Enable/disable the Legacy USB support fuction. AUTO option disables legacy support if no USB devices are connected. DISABLE option will keep USB devices available only for EFI applications.

Options available: Enabled/Disabled/Auto. Default setting is Enabled.

####

This is a workaround for OSes without XHCl hand-off support. The XHCl ownership change should be claimed by XHCl driver.

Options available: Enabled/Disabled. Default setting is Enabled.

# USB Mass Storage Driver Support<sup>(Note)</sup>

Enable/Disable the USB Mass Storage Driver Support.

Options available: Enabled/Disabled. Default setting is Enabled.

### → Port 60/64 Emulation

Enables the I/O port 60h/64h emulation support. This should be enabled for the complete USB Keyboard Legacy support for non-USB aware OSes.

Options available: Enabled/Disabled. Default setting is Enabled.

## USB hardware delays and time-outs:

### → USB transfer time-out

The time-out value for Control, Bulk, and Interrupt transfers.

Options available: 1 sec/5 sec/10 sec/20 sec. Default setting is 20 sec.

(Note) This item is present only if you attach USB devices.

## → Device reset time-out

USB mass storage device Start Unit command time-out.

Options available: 10 sec/20 sec/30 sec/40 sec. Default setting is **20 sec**.

### ○ Device power-up delay

Maximum time the device will take before it properly reports itself to the Host Controller. "Auto" uses default value: for a Root port it is 100 ms, for a Hub port the delay is taken from Hub descriptor. Options available: Auto/Manual. Default setting is **Auto**.

# 5-2-7 AST2500 Super IO Configuration

- → AST2500 Super IO Configuration

Displays the super IO chip information.

Serial Port 1/2 Configuration

Press [Enter] for configuration of advanced items.

# 5-2-7-1 Serial Port 1/2 Configuration

- Serial Port 1/2 Configuration

- → Serial Port<sup>(Note1)</sup>

Enable/Disable the Serial Port (COM). When set to Enabled allows you to configure the Serial port 1/2 settings. When set to Disabled, displays no configuration for the serial port.

Options available: Enabled/Disabled. Default setting is Enabled.

□ Devices Settings<sup>(Note2)</sup>

Displays the Serial Port 1/2 device settings.

(Note1) Advanced items prompt when this item is defined. (Note)

(Note2) This item appears when Serial Port is set to Enabled

# ○ Change Settings(Note2)

Select an optimal settings for Super IO Device.

Options available for Serial Port 1:

Auto

IO=3F8h; IRQ=4;

IO=3F8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12;

IO=2F8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12;

IO=3E8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12;

IO=2E8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12;

Default setting is Auto.

Options available for Serial Port 2:

Auto

IO=2F8h: IRQ=3:

IO=3F8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12;

IO=2F8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12;

IO=3E8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12;

IO=2E8h; IRQ=3, 4, 5, 6, 7, 9, 10, 11, 12;

Default setting is Auto.

Please note that this item is configurable when Serial Port is set to Enabled.

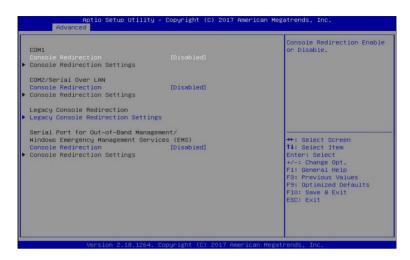

## 5-2-8 Serial Port Console Redirection

# ○ COM1/COM2 Serial Over LAN Console Redirection<sup>(Note)</sup>

Select whether to enable console redirection for the specified device. Console redirection enables the users to manage the system from a remote location.

Options available: Enabled/Disabled. Default setting is Disabled.

## □ Legacy Console Redirection

Selects a COM port for Legacy serial redirection. The options are dependent on the available COM ports.

# Serial Port for Out-of-Band Management/Windows Emergency Management Services (EMS) Console Redirection<sup>(Note)</sup>

Selects a COM port for EMS console redirection. EMS console redirection allows the user to configure Console Redirection Settings to support Out-of-Band Serial Port management.

Options available: Enabled/Disabled. Default setting is Disabled.

# COM1/COM2 Serial Over LAN/Legacy/Serial Port for Out-of-Band EMS Console Redirection Settings

Press [Enter] for configuration of advanced items.

Please note that this item is configurable when COM1/COM2 Serial Over LAN/Serial Port for Outof-Band Management EMS Console Redirection is set to Enabled.

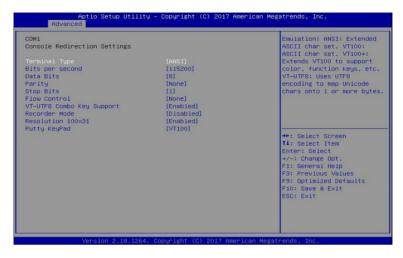

# 5-2-8-1 COM1/COM2 Serial Over LAN/Legacy/Serial Port for Out-of-Band EMS Console Redirection Settings

# COM1/COM2 Serial Over LAN Console Redirection Settings

## Terminal Type

Selects a terminal type to be used for console redirection.

Options available: VT100/VT100+/ANSI /VT-UTF8. Default setting is ANSI.

#### Bits per second

Selects the transfer rate for console redirection.

Options available: 9600/19200/38400/57600/115200. Default setting is 115200.

## Data Bits

Selects the number of data bits used for console redirection.

Options available: 7/8. Default setting is 8.

## → Parity

A parity bit can be sent with the data bits to detect some transmission errors.

Even: parity bit is 0 if the num of 1's in the data bits is even.

Odd: parity bit is 0 if num of 1's in the data bits is odd.

Mark: parity bit is always 1. Space: Parity bit is always 0.

Mark and Space Parity do not allow for error detection.

Options available: None/Even/Odd/Mark/Space. Default setting is None.

## → Stop Bits

Stop bits indicate the end of a serial data packet. (A start bit indicates the beginning). The standard setting is 1 stop bit. Communication with slow devices may require more than 1 stop bit.

Options available: 1/2. Default setting is 1.

#### → Flow control

Flow control can prevent data loss from buffer overflow. When sending data, if the receiving buffers are full, a 'stop' signal can be sent to stop the data flow. Once the buffers are empty, a 'start' signal can be sent to re-start the flow. Hardware flow control uses two wires to send start/stop signals.

Options available: None/Hardware RTS/CTS. Default setting is None.

##

Enable/Disable the VT-UTF8 Combo Key Support.

Options available: Enabled/Disabled. Default setting is Enabled.

## → Recorder Mode<sup>(Note)</sup>

When this mode enabled, only texts will be send. This is to capture Terminal data.

Options available: Enabled/Disabled. Default setting is Disabled.

#### → Resolution 100x31<sup>(Note)</sup>

Enable/Disable extended terminal resolution.

Options available: Enabled/Disabled. Default setting is Enabled.

# → Putty KeyPad<sup>(Note)</sup>

Selects FunctionKey and KeyPad on Putty.

Options available: T100/LINUX/XTERMR6/SCO/ESCN/VT400. Default setting is VT100.

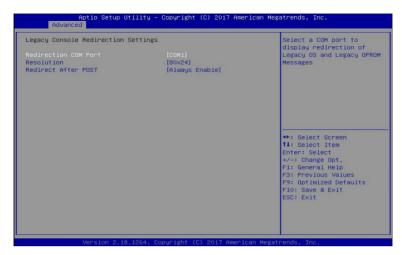

## Legacy Console Redirection Settings

## □ Redirection COM Port

Selects a COM port to display redirection of Legacy OS and Legacy OPROM Messages.

Options available: COM1/COM2 Serial Over LAN. Default setting is COM1.

#### Resolution

On Legacy OS, the Number of Rows and Columns supported redirection.

Options available: 80x24/80x25. Default setting is 80x24.

#### Redirect After POST

When Bootloader is selected, then Legacy Console Redirection is disabled before booting to legacy OS.

When Always Enable is selected, then Legacy Console Redirection is enabled for legacy OS.

Options available: Bootloader/Always Enable. Default setting is **Always Enable**.

#

# ○ Out-of-Band Mgmt Port

Microsoft Windows Emerency Management Service (EMS) allows for remote management of a Windows Server OS through a serial port.

Options available: COM1/COM2 Serial Over LAN. Default setting is COM1.

# 5-2-9 PCI Subsystem Settings

#### → PCI Bus Driver Version

Displays the PCI Bus Driver version information.

## PCI Devices Common Settings:

## → PCI Latency Timer

Sets the value to be programmed into PCI Latency Timer Register.

Options available: 32 PCI Bus Clocks/64 PCI Bus Clocks/96 PCI Bus Clocks/128 PCI Bus Clocks/160 PCI Bus Clocks/192 PCI Bus Clocks/224 PCI Bus Clocks/248 PCI Bus Cloc

Default setting is 32 PCI Bus Clocks.

## → PCI-X Latency Timer

Sets the value to be programmed into PCI-X Latency Timer Register.

Options available: 32 PCI Bus Clocks/64 PCI Bus Clocks/96 PCI Bus Clocks/128 PCI Bus Clocks/160 PCI Bus Clocks/192 PCI Bus Clocks/224 PCI Bus Clocks/248 PCI Bus Cloc

Default setting is 64 PCI Bus Clocks.

## VGA Palette Snoop

Enable/Disable VGA Palette Registers Snooping.

Options available: Enabled/Disabled. Default setting is Disabled.

#### → PERR#/SERR# Generation

Enable/Disable PCI Device to Generate PERR#/SERR#.

Options available: Enabled/Disabled. Default setting is Disabled.

## Above 4G Decoding

Enable/Disable 64-bit capable Devices to be decoded in Above 4G Address Space (Only if System Supports 64 bit PCI Decoding).

Options available: Enabled/Disabled. Default setting is Enabled.

# SR-IOV Support

If the system has SR-IOV capable PCIe devices, this item Enable/Disable Single Root IO Virtualization Support.

Options available: Enabled/Disabled. Default setting is **Disabled**.

## 5-2-10 Network Stack

#### Network stack

Enable/Disable the UEFI network stack.

Options available: Enabled/DIsabled. Default setting is Enabled.

## → Ipv4 PXE Support<sup>(Note)</sup>

Enable/Disable the Ipv4 PXE feature.

Options available: Enabled/DIsabled. Default setting is **Enabled**.

# → Ipv4 HTTP Support<sup>(Note)</sup>

Enable/Disable the Ipv4 HTTP feature.

Options available: Enabled/DIsabled. Default setting is Disabled.

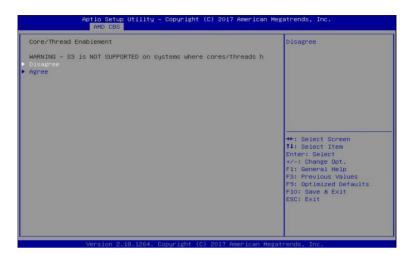

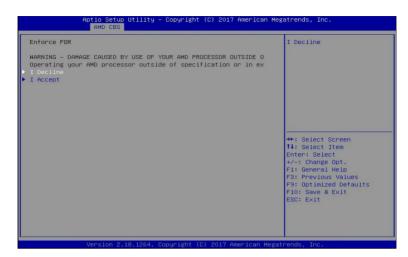

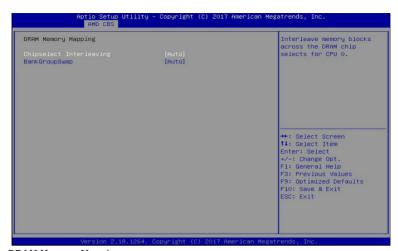

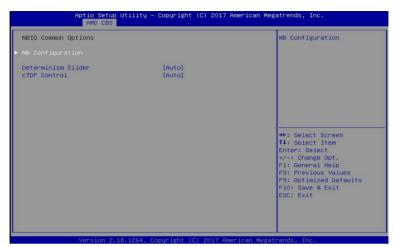

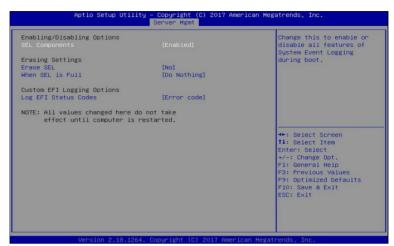

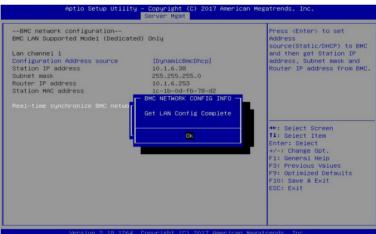

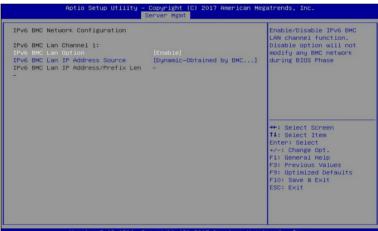

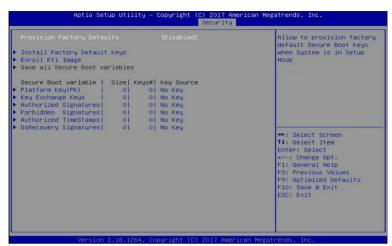

## → Ipv6 PXE Support<sup>(Note)</sup>